# EDEC Chip Design Contest

## 뉴로모픽 소자 개발을 위한 Array TEG 설계 및 분석

최현웅, 김성현, 송기우, \*이희덕 *충남대학교 전자공학과*

#### 서론

- 새로운 소자 혹은 Technology 개발은 수많은 TEG를 통해서 이루어져 왔음.

- 신소자를 개발하기 위해서는 대량의 신소자 데이터를 통계적으로 분석하는 것이 필수적임.

- 따라서 본 논문에서는 대량의 신소자 데이터를 고속으로 확보 가능한 TEG를 설계하였음.

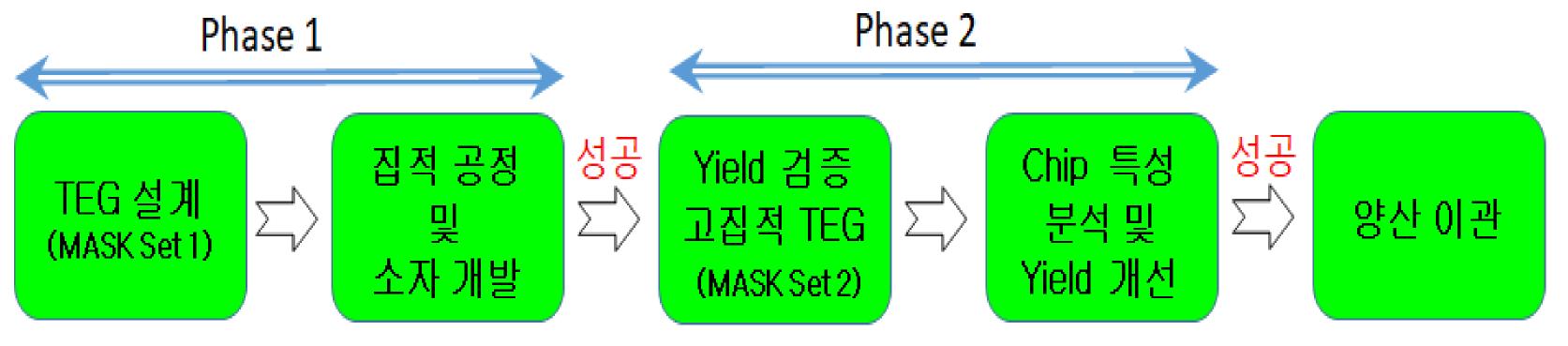

<그림 1. 일반적인 신소자 개발 단계>

#### 본론

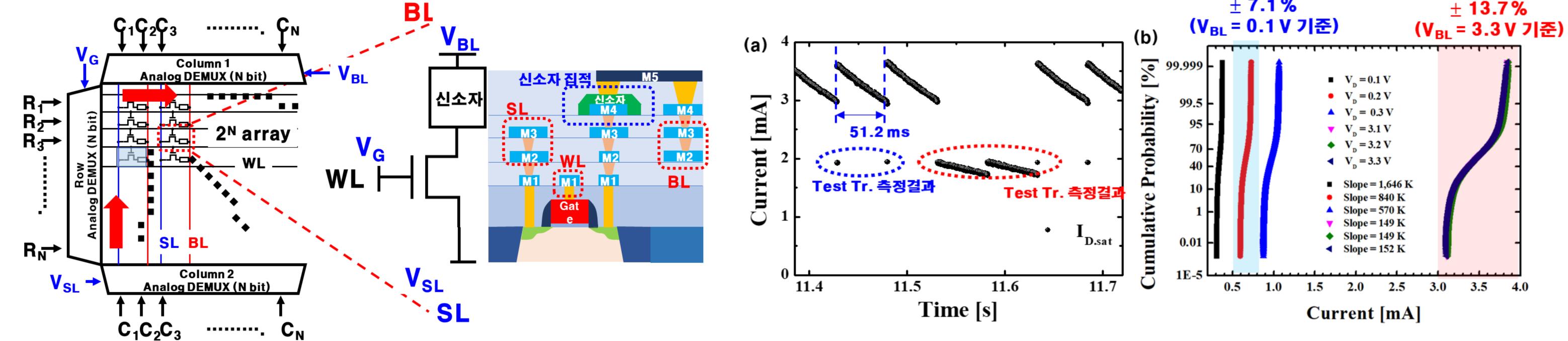

- 신소자 Array의 전기적 특성 분석을 위하여 Analog DEMUX와 Cell Array로 TEG를 구성하였음 〈그림 2〉

- 대량 (25 만개 이상) 데이터를 단시간 (2 분) 이내에 확보할 수 있도록 Sampling interval을 100  $\mu$ s로 측정하였으며 〈그림 3(a)〉,  $V_{BL}$  = 0.1 V 기준  $\pm$  8 % 미만의 낮은 Variation을 보임 〈그림 3(b)〉.

〈그림 2. 대용량 고속 Array TEG 구성도와 집적 단면도 예시〉

〈그림 3. Array TEG 평가결과, (a) I/V-t sampling, (b) Cumulative distribution of V<sub>BI</sub> split>

### 결론

- 실제 측정시스템과 연동하여 대량의 데이터 (25 만개 이상)를 고속 (< 2 분)으로 측정 가능함을 보여 TEG 자체 효용성을 검증하였음.

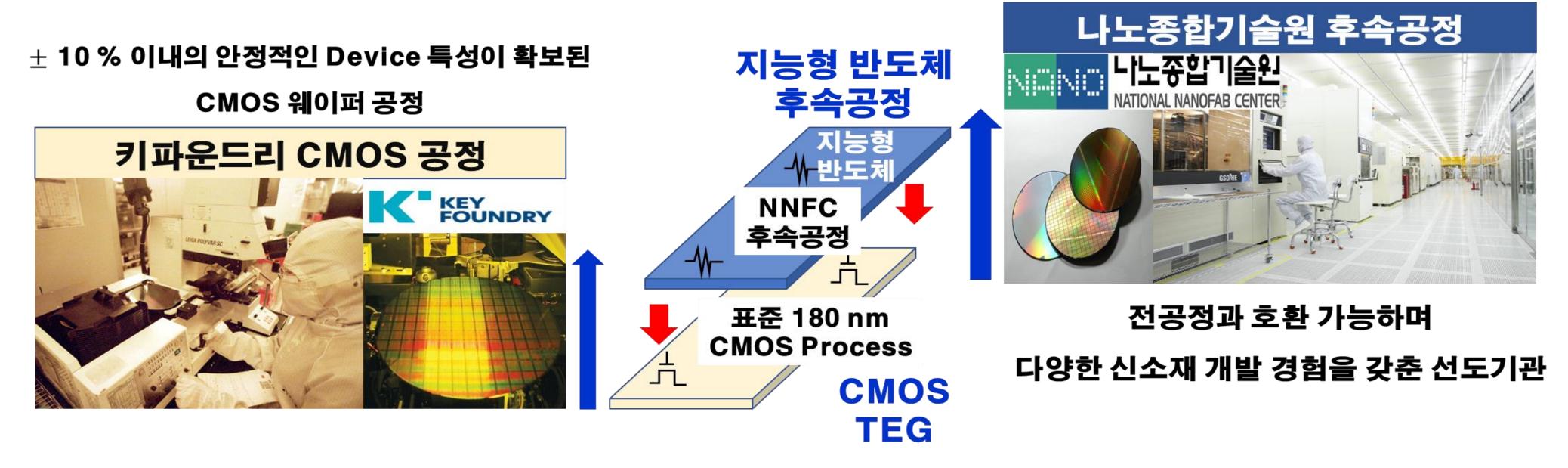

- 제작된 TEG 웨이퍼 위에 〈그림 4〉와 같이 후속공정으로 지능형 반도체를 집적할 경우, 대량의 데이터를 통계적으로 분석할 수 있는 플랫폼으로써 활용 가능할 것으로 기대함.

<그림 4. Hybrid 집적공정 모식도>

- Acknowledgement

- The chip fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.

- This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (NRF-2019M3F3A1A01074449).